# Preventing timing information leakages from the microarchitecture

By Mathieu Escouteloup (Inria) Advisors: Ronan Lashermes (Inria) Christophe Bidan (CentraleSupélec) Jacques Fournier (CEA-Leti)

March 30, 2020

### Table of contents

Shared resources

- 2 ISA contextualization

- 3 Timing evaluation

- Conclusion

- Shared resources

- 2 ISA contextualization

- Conclusion

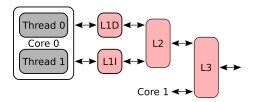

## Microarchitectural sharing

#### Definition

- Multiple entities can request the same resource.

- Entities: hardware threads, cores, processes ...

- Resources: cache memories, prediction tables, FSMs, buffers ...

#### Two kinds of sharing

- Temporal: use the same resource but at different points in time.

- Spatial: use the same resource at the same time.

- Both can be combined.

Data but also timing informations are shared between the entities.

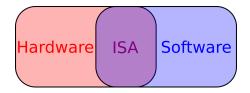

# An implementation issue ...

Shared resources 0000

- Targeted shared resources are in the microarchitecture.

- Leakages depend on the implementation.

- Microarchitecture cannot be controlled by the software.

... but not only!

- Shared resources

- 2 ISA contextualization

- Conclusion

- Which part knows the application logic?

- Which part can efficiently make the isolation?

- How can they exchange information?

The whole system is concerned!

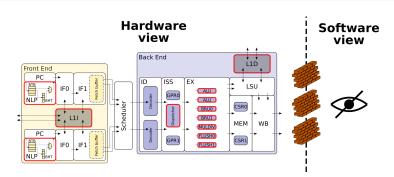

## How to modify the ISA?

#### Constraints:

- Consider the whole isolation issue: temporal and spatial sharing.

- 2 Create custom security domains.

- Scalability to multiple systems.

- Preserve the architecture abstraction

Contextualization: associate a domain to each data and resource.

## Our security domain model.

#### New dedicated register:

• identifier: an unique number for each security domain.

#### New instruction: CONTEXT.SWITCH.

- Indicates a domain change.

- Some actions must be done:

- Flush traces from the old domain.

- 2 Split resources if needed.

- 1 Lock resources if needed.

- Successful  $\rightarrow$  a new domain can be safely executed.

15. ... 16. ...

```

# OLD CONTEXT

old-app:

3.

4.

10. switch-code:

11. csrw nextid,a0 # config

12. switch a0

# switch

13. # NEW CONTEXT

14. new-app:

```

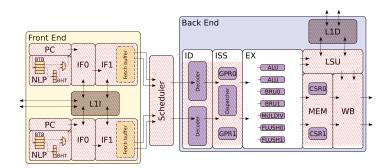

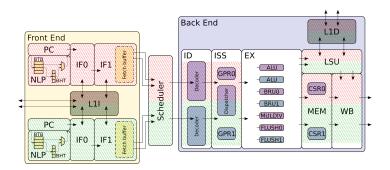

### Hardware view: after switch.

Successfully implemented in two cores, one with SMT.

Timing evaluation •000

### Table of contents

- Shared resources

- 2 ISA contextualization

- 3 Timing evaluation

- Conclusion

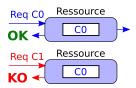

Timing evaluation 0000

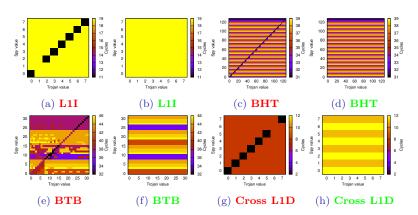

## An implementation agnostic benchmark

#### Goal:

to quantitatively evaluate information leakages in the microarchitecture.

#### Constraints:

- focus on timing information leakages in the design,

- consider common shared resources,

- focus on vulnerability, not exploitability.

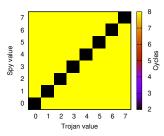

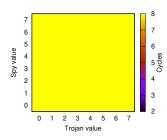

#### Scenario:

- a trojan encodes a value in a shared resource state,

- a spy tries to recover the value.

# The cache example: temporal sharing

(a) Unprotected L1D

Timing evaluation 0000

(b) Protected L1D

Timing evaluation 0000

More under development ...

- Shared resources

- ② ISA contextualization

- 3 Timing evaluation

- 4 Conclusion

### Conclusion

- Shared resources are sources of vulnerability.

- The ISA must be modified to give security information to the hardware.

- Software indicates its constraints, hardware applies them.

- A new security benchmark to evaluate the implementations.

**Timesecbench:** https://gitlab.inria.fr/rlasherm/timesecbench