Abondance core

Abondance is a french breed of cows from the Haute-Savoie in the south-east of France. It is mainly raised for its milk used in multiple cheeses like the Reblochon, the Abondance and others.

This page and the following ones describe the Abondance core. It is a multiple issue out-of-order CPU with two levels of cache memories.

Overview

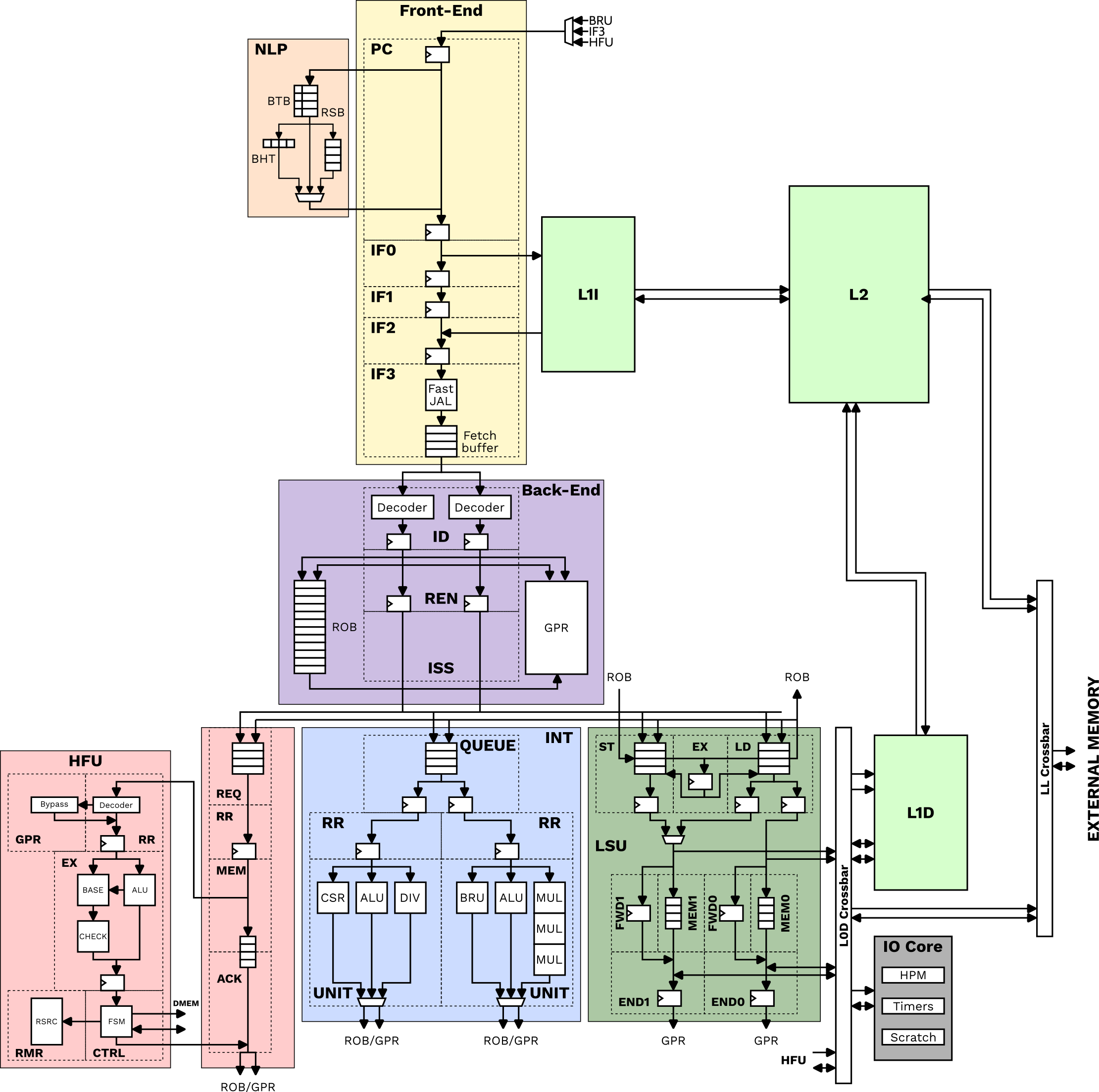

The Figure 1 represents the whole Abondance core.

It is composed of 10 parts.

The Front-End is responsible for the instruction fetch.

The NLP is used to predict control-flow changes.

The Back-End is responsible for the decoding and the execution management.

It also integrates renaming mechanisms used by multiple units for integers.

The INT is responsible for the execution of integer operation.

The LSU is responsible for the execution of integer memory operations.

The Hardware Field Unit (HFU) is an execution unit dedicated to field management (CHAMP ISA).

The I/O module is used for core’s specific memory addressable mechanism (e.g. privileged timers).

L1I, L1D and L2 are respectively the Level 1 Instruction, Level 1 Data and the Level 2 (Instruction and Data) private cache memories.

ISA support

The Abondance core is based on the RISC-V ISA. It currently supports both 32 and 64 bits bases.

| Extension | Version | Implemented ? | Tested ? | Optional ? | Dependencies |

|---|---|---|---|---|---|

| M | 2.0 | ||||

| A | 2.1 | ||||

| B | 1.0.0 | ||||

| Zicsr | |||||

| Zicntr | |||||

| Zifencei | 2.0 |

As described on the Table 1, multiple extensions are currently implemented in the Abondance. Most of them are optional: the dedicated hardware parts are completely removed during Verilog generation.

If both 32 and 64 bits are implemented, only 32 bits version is currently used and tested. More work is needed to verify 64 bit specific instructions, like ones dedicated to word-size datas.